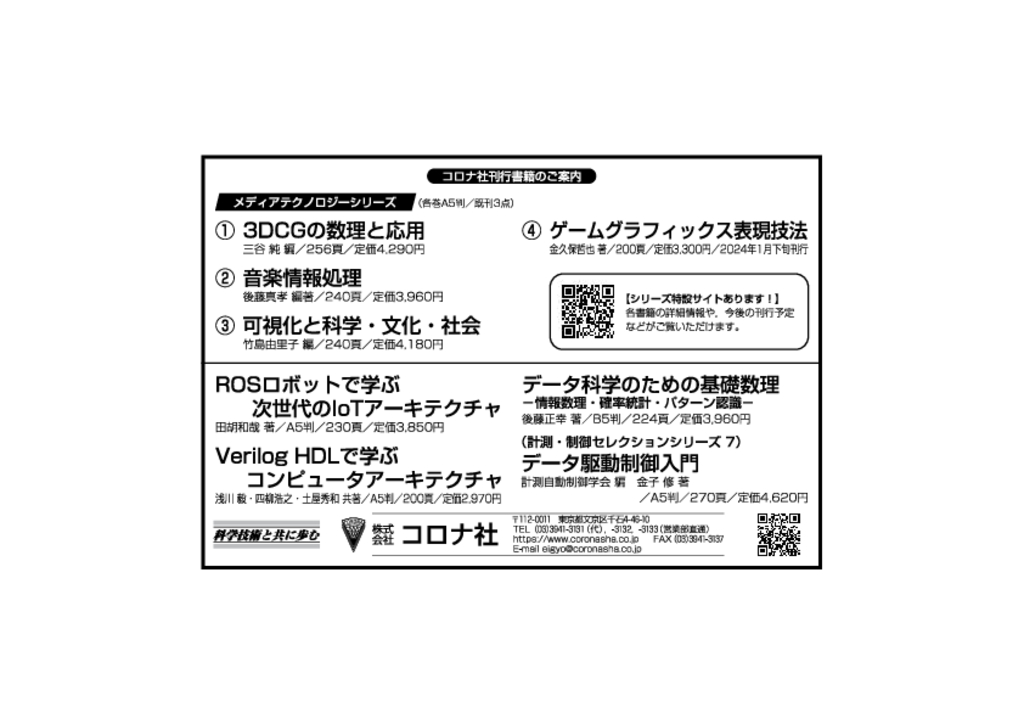

Verilog HDLで学ぶコンピュータアーキテクチャ

Web公開のコード等で独習も可能な,HDLによる実践的なディジタル回路設計の入門書

- ジャンル

- 発行年月日

- 2024/02/20

- 判型

- A5

- ページ数

- 200ページ

- ISBN

- 978-4-339-02940-6

- 内容紹介

- まえがき

- 目次

- 広告掲載情報

近年の開発現場ではハードウェア記述言語(HDL)を用いてディジタル回路設計を行うことが一般的になっている。

本書「Verilog HDLで学ぶコンピュータアーキテクチャ」ではコンピュータアーキテクチャの理解をテーマとして,ハードウェア記述言語(HDL)によるディジタル回路設計技術を学ぶことが出来るように構成されている。

また独習者に向けて書籍内でとりあげたすべてのハードウェア記述言語(HDL)によるコードや,回路のFPGAへの実装方法をコロナ社HP上で公開している。

さらに各章に演習問題を用意し、理解度を確認出来るようになっている。

近年の開発現場では,ハードウェア記述言語(HDL)を用いてディジタル回路設計を行うことが一般的になっている。しかし,ディジタル回路設計技術を教える工学系大学では,論理回路による基本的設計技術の教授に留まり,それに続く実践的なHDLを用いた設計について,多くは展開できていない現状にある。そうした中にあって,著者らはLSIの設計・評価を研究のメインテーマとして取り組んでいる。関連するLSIメーカとの技術交流を通して,大学でのHDLを用いたディジタル回路設計技術教育の必要性を感じ,講義やゼミ等で実践的教育を行っている。

本書は,コンピュータアーキテクチャの理解をテーマとして,HDLによるディジタル回路設計技術を学ぶ教科書として構成した。2進数や論理回路などの基本的なコンピュータ工学の基礎は他書に譲り,内容を進めている。また,本書による独習も想定し,とりあげたすべてのHDLによるコードは,学習を進める上でそのまま利用できるようにコロナ社Webサイト(https://www.coronasha.co.jp/np/isbn/9784339029406/)で公開しており,回路のFPGAへの実装方法(第11章)についても解説している。各章には理解度を確認するための演習問題を用意したので,活用していただきたい。

本書を実践的なディジタル回路設計の入門書として,学生や社会人の方々に幅広く利用いただき,技術力向上の一助となれば,著者一同,この上ない喜びである。

2023年12月

著者を代表して 浅川毅

第1章 コンピュータアーキテクチャ

1.1 コンピュータの基本構成

1.1.1 プログラム内蔵方式

1.1.2 コンピュータの基本構成

1.2 コンピュータの動作原理

1.2.1 CPUとメモリ構成

1.2.2 命令の実行

1.3 汎用コンピュータの動作の流れ

演習問題

第2章 マイクロプロセッサとメインメモリ

2.1 マイクロプロセッサ

2.1.1 マイクロプロセッサの分類

2.1.2 マイクロプロセッサの基本構成

2.1.3 直接制御方式

2.1.4 間接制御方式

2.2 マイクロプロセッサの特性の尺度

2.3 メモリ

2.3.1 記憶階層

2.3.2 メモリの基本構成

2.3.3 メモリの特性

2.3.4 メモリの分類

演習問題

第3章 コンピュータの表現と実装

3.1 論理と電気的特性

3.1.1 ビットとバイト

3.1.2 文字の表現

3.1.3 数値の表現

3.1.4 負数の表現

3.1.5 論理電圧

3.2 ステートマシンの表現

3.2.1 ステートマシン

3.2.2 状態割当

3.2.3 状態遷移の制御

3.2.4 出力関数の違いによるステートマシンの分類

3.3 コンピュータの実装法

3.4 FPGAの概要

演習問題

第4章 Verilog HDLによる回路設計

4.1 ハードウェア記述言語を用いる設計の概要

4.2 Verilog HDLによる論理設計

4.2.1 Verilog HDLを使用した設計の流れ

4.2.2 モジュールの記述

4.2.3 数値と信号の表現

4.2.4 回路記述方法

4.2.5 回路構成例

4.3 Verilog HDLによるシミュレーション

演習問題

第5章 レジスタ,カウンタ要素

5.1 フリップフロップと順序回路

5.2 レジスタ

5.2.1 レジスタの回路構成

5.2.2 コンピュータで使用する各種レジスタ

5.2.3 シフトレジスタ

5.3 カウンタ

5.4 レジスタのVerilog HDL記述例

5.5 シフトレジスタのVerilog HDL記述例

5.6 シフトレジスタのVerilog HDL記述例

5.7 カウンタのVerilog HDL記述例

5.8 カウンタのVerilog HDL記述例

演習問題

第6章 演算要素

6.1 演算装置

6.1.1 加算器

6.1.2 比較器

6.1.3 シフト演算器

6.1.4 乗算器

6.1.5 データバスとALUの接続

6.2 演算装置のVerilogHDL記述例

6.3 加算器のVerilogHDL記述例

6.3.1 半加算器

6.3.2 全加算器

演習問題

第7章 制御要素

7.1 デコーダとエンコーダ

7.2 マルチプレクサとデマルチプレクサ

7.3 制御回路の実装方式

7.4 デコーダのVerilog HDL記述例

7.5 エンコーダのVerilog HDL記述例

7.6 マルチプレクサのVerilog HDL記述例

7.7 デマルチプレクサのVerilog HDL記述例

演習問題

第8章 コンピュータの命令

8.1 命令と機械語

8.2 命令サイクル

8.3 命令の形式

8.4 アドレスの指定

8.5 代表的な命令

8.5.1 データ転送命令

8.5.2 演算命令

8.5.3 比較命令

8.5.4 シフト命令

8.5.5 プログラム制御命令

演習問題

第9章 コンピュータの高速化技術と信頼性

9.1 マルチプログラミング

9.2 キャッシュメモリ

9.2.1 キャッシュメモリの役割

9.2.2 キャッシュメモリの構成

9.2.3 キャッシュデータの更新

9.3 マルチバンク

9.4 パイプライン

9.4.1 パイプライン処理の原理

9.4.2 パイプラインハザード

9.4.3 スーパーパイプライン

9.5 並列処理

9.5.1 スーパースカラ

9.5.2 VLIW

9.5.3 マルチプロセッサ

9.5.4 マルチコアプロセッサ

9.6 コンピュータシステムの信頼性

9.6.1 RAS

9.6.2 MTBF

9.6.3 MTTR

9.6.4 稼働率

9.6.5 システムの稼働率

演習問題

第10章 FPGAによるメモリのアクセス

10.1 メモリの構成

10.2 メモリコントローラの記述例

10.3 メモリ機能チェックシステムの構築

演習問題

第11章 FPGAへの実装(コロナ社Webサイトにて公開)

付録:設計に用いる命令セット一覧

引用・参考文献

索引

-

掲載日:2024/10/01

-

掲載日:2024/03/12

-

掲載日:2024/02/05

-

掲載日:2024/01/17

関連資料(一般)

- 第11章 FPGAへの実装

- 演習問題解答(24.7.23更新)

- 本書でとりあげたHDLによるコード