デジタル回路設計入門 - FPGA時代の論理回路設計 -

FPGAの論理設計の基礎学習に最適な,回路設計技術者によるノウハウも取り入れた入門書

- 発行年月日

- 2021/04/26

- 判型

- A5

- ページ数

- 190ページ

- ISBN

- 978-4-339-00943-9

- 内容紹介

- まえがき

- 目次

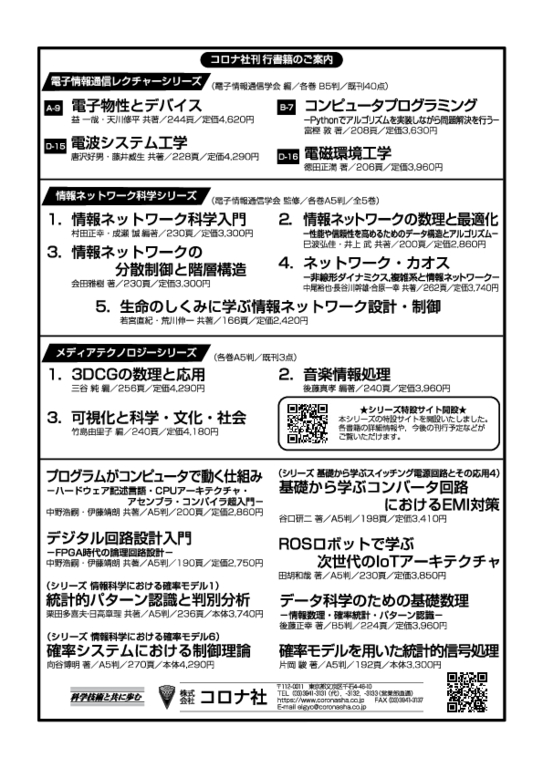

- 広告掲載情報

回路計算量の考え方や設計時の注意点,実装方法など,実際に回路設計を行っている技術者によるノウハウも取り入れた入門書。FPGAの設計を意識した内容となっており,初心者から実務者まで幅広い読者に有益な内容となっている。

『1章 論理式と組み合わせ回路』では,真理値を対象とする論理関数を表すのに使われる真理値表,論理式,組み合わせ回路という三つの表現方法の取り扱いと相互の変換方法がテーマとなっている。

『2章 さまざまな組み合わせ回路』では,実際の論理回路でよく用いられるスリーステートバッファ回路,セレクタ回路,デコーダ回路,バレルシフト回路の設計方法がテーマとなっている。

『3章 算術演算回路』では,ビット列で負の数を表現するための方法と,加算・減算・乗算を行うための組み合わせ回路や,演算結果のオーバーフローの判定方法が主なテーマとなっている。

『4章 記憶回路』では,真理値を記憶するのに用いられるフリップフロップの構成方法,正しく動作するための条件をテーマとなっている。

『5章 順序回路』では,記憶回路のフリップフロップ(レジスタ)と組み合わせ回路を用いた論理回路である順序回路をテーマとなっている。

『6章 実用的な回路』では,ここまで紹介されてきた組み合わせ回路と順序回路の知識をベースにした実用的回路の設計をテーマとなっている。

本書は,デジタル回路設計を初めて学ぶ大学の学部生を対象とした教科書である。前提となる知識は高校の数学I程度のレベルであり,高校生が読んでも理解できるように書かれている。

ほかの一般的なデジタル回路設計や論理設計の教科書と違い,プログラマブル集積回路であるFPGAの設計を意識した内容になっており,実際のデジタル回路設計の際に考慮しなければならない事柄について,詳しく説明している。また,理論的な回路計算量の考え方も含んでいる。すでにデジタル回路設計を学んだ大学院生や社会人が読んでも,デジタル回路設計に関する新たな知識を得られるようになっている。実際にデジタル回路設計を行っている技術者が経験によって獲得し,意識せずに用いているノウハウ的な内容も含んでおり,そのような技術者にとっても本書を読むことは有益である。

本書は6章で構成される。

1章は,論理式と,基本ゲート回路を用いた組み合わせ回路について説明している。カルノー図やクワイン・マクラスキー法を用いた論理式の簡単化がおもな内容である。論理関数の表現方法として,真理値表,論理式,組み合わせ回路の3通りがあるが,これらが相互に変換可能であることを説明している。これらの内容に加えて,汎2入力ゲートとそれを用いた組み合わせ回路の大きさの評価法について述べている。これは回路計算量を理論的に議論するベースとなる。

2章は,よく使われるさまざまな組み合わせ回路について紹介している。特に,実際の回路でよく用いられるセレクタ回路とデコーダ回路の設計方法について詳しく説明している。これらに加えて,セレクタ回路と汎2入力ゲートを用いた任意のnビット論理関数を計算する回路の構成法を説明している。これは他書にない特徴的な内容で,回路計算量理論の基礎となる考え方を示している。

3章は,整数や小数点数のビット列による表現方法と,加算回路,減算回路,乗算回路の設計方法について説明している。特に,オーバーフローの判定法や2の補数の場合の乗算回路についても紹介している。

4章は,ラッチやフリップフロップ等の記憶回路を基本ゲート回路を用いて構成する方法について紹介している。また,フリップフロップのアクセスタイム,セットアップタイム,ホールドタイム等の時間定数について説明しており,フリップフロップが正しく動作するための条件を示している。また,フリップフロップを用いた最も簡単な回路の例として,非同期カウンタ回路を説明している。

5章は,フリップフロップと組み合わせ回路を用いた順序回路の設計法である。まず,2^n進カウンタの設計法と,最大動作周波数の求め方を説明している。続いて,2のべきでないカウンタの例として5進カウンタの設計法を示しているが,多くの人により共通して行われている間違った設計法を紹介し,正しく動作しない理由を説明している。そして,改めて正しい5進カウンタの設計法を示している。FPGA等でよく用いられる順序回路である完全同期式順序回路をミーリー型,ムーア型,単純型の3通りに分類し,それらの特徴について解説している。また,完全同期式順序回路のレジスタトランスファレベルシミュレーションとゲートレベルシミュレーションについて解説し,正しく動作するための条件を示している。具体的な完全同期式順序回路の例として,ステートマシンとメモリ回路を紹介している。

6章は,いくつかの実用的な回路を紹介している。数取器回路を題材に,外部からの入力信号を受け付ける順序回路の設計時に注意すべき点について説明している。また,FPGAに組み込まれているルックアップテーブル回路とその使い方について述べている。最後に畳み込み回路の設計と,パイプライン化による高速化手法,およびFPGAが組み込んでいるDSP回路を用いた畳み込み回路の実装方法について紹介している。

以上により,実践的なデジタル回路設計やFPGAの設計を行うにあたり,基礎的な内容をマスターでき,また,回路計算量の理論的な分析も行えるようになる。

最後に,本書を出版するにあたり,コロナ社に深く感謝を申し上げる。

2021年2月

中野浩嗣,伊藤靖朗

1.論理式と組み合わせ回路

1.1 論理式,組み合わせ回路,および論理関数

1.1.1 論理演算の基本法則

1.1.2 基本ゲート回路と組み合わせ回路

1.1.3 基本ゲート回路の拡張と排他的論理和

1.1.4 汎2入力ゲートと組み合わせ回路の大きさ

1.2 論理式と組み合わせ回路の簡単化

1.2.1 論理式の標準形

1.2.2 論理演算の基本法則を用いた論理式の簡単化

1.2.3 カルノー図

1.2.4 カルノー図を用いた論理式の簡単化

1.2.5 禁止入力付き論理関数とカルノー図

1.2.6 7セグメントデコーダ回路

1.2.7 クワイン・マクラスキー法による論理式の簡単化

1.2.8 5変数以上のカルノー図

1.2.9 NANDゲートだけ,もしくはNORゲートだけを用いた組み合わせ回路

演習問題

2.さまざまな組み合わせ回路

2.1 2進数

2.2 スリーステートバッファ回路とバス

2.3 セレクタ回路

2.3.1 2入力セレクタ回路

2.3.2 多入力セレクタ回路

2.3.3 多入力セレクタ回路の再帰的設計

2.3.4 セレクタ回路を用いた任意の論理関数計算回路

2.3.5 セレクタ回路による論理関数計算回路の大きさ削減

2.4 デコーダ回路

2.4.1 積和形の論理式によるデコーダ回路

2.4.2 再帰的設計によるデコーダ回路

2.4.3 デコーダ回路を用いたセレクタ回路

2.5 バレルシフト回路

演習問題

3.算術演算回路

3.1 符号付き2進数

3.1.1 符号付き絶対値表現

3.1.2 1の補数表現

3.1.3 2の補数表現

3.1.4 ビット拡張

3.2 インクリメント回路

3.3 加算回路

3.3.1 符号なし2進数の加算回路

3.3.2 2の補数の加算回路

3.4 減算回路

3.5 乗算回路

3.5.1 符号なし2進数の乗算回路

3.5.2 2の補数の乗算回路

3.6 小数点数

3.6.1 固定小数点数

3.6.2 固定小数点数の算術演算回路

3.6.3 浮動小数点数

演習問題

4.記憶回路

4.1 フリップフロップの構造

4.1.1 RS型フリップフロップ

4.1.2 D型ラッチ

4.1.3 D型フリップフロップ

4.1.4 非同期セット・非同期リセット付きD型フリップフロップ

4.1.5 nビットフリップフロップ(レジスタ)

4.1.6 イネーブル付きフリップフロップ

4.2 フリップフロップの時間定数

4.2.1 セットアップタイム・ホールドタイムとメタステーブル状態

4.2.2 最小アクセスタイム・最大アクセスタイム

4.3 フリップフロップを用いた回路

4.3.1 T型フリップフロップ

4.3.2 非同期カウンタ回路

演習問題

5.順序回路

5.1 カウンタ回路

5.1.1 カウンタ回路の設計

5.1.2 レジスタトランスファレベルシミュレーション

5.1.3 ゲートレベルシミュレーション

5.1.4 クロックスキュー

5.1.5 カウンタ回路の動作周波数

5.2 2のべきでないカウンタ回路

5.2.1 間違った設計方法

5.2.2 正しい設計方法

5.3 完全同期式順序回路

5.4 ステートマシンとワンホットステートマシン

5.4.1 ムーア型完全同期式順序回路によるステートマシンの設計

5.4.2 ステートマシンのハザード

5.4.3 単純型完全同期式順序回路によるステートマシンの設計

5.4.4 ワンホットステートマシンの設計

5.5 メモリ回路

5.5.1 メモリ回路の仕様

5.5.2 メモリ回路の設計

演習問題

6.実用的な回路

6.1 積分回路と微分回路

6.1.1 積分回路

6.1.2 微分回路と立ち上がり検出回路

6.2 数取器回路

6.2.1 立ち上がり検出回路を用いた数取器回路

6.2.2 メタステーブル対策を行った数取器回路

6.2.3 チャタリング除去回路

6.3 ルックアップテーブル回路

6.3.1 5LUT2による2ビット加算器

6.3.2 6LUT1による4入力セレクタ回路

6.3.3 6LUT1を用いた論理関数計算回路

6.4 畳み込み計算回路

6.4.1 畳み込み計算回路の設計

6.4.2 畳み込み計算回路の性能評価

6.4.3 組み合わせ回路のパイプライン化による高速化

6.4.4 DSP回路を用いた畳み込み計算回路

演習問題

索引

-

掲載日:2024/03/12

-

掲載日:2022/10/03

-

掲載日:2021/09/30

-

掲載日:2021/09/27

-

掲載日:2021/06/01