####

問題のデータパス部に含まれる各部分回路は下記の機能を持つ.

- 1: 4 ビットのシフトレジスタ SR-a および SR-b は、以下の 4 つの機能を有する.

- (00) 格納している 4 ビットを変えない

- (01) 4ビットの入力を同時に取り込む

- (10) 左に 1 ビットシフトし, 最下位ビットに入力 IR を取り込む

- (11) 右に 1 ビットシフトし、最上位ビットに入力  $I_L$ を取り込む

- 2: 全加算器 FA は, 4 つの 1 ビット入力 a, b, c の加算をし, carry と sum の各 1 ビットを出力する. 従って, 図に示された接続関係から, SR-a に格納された 4 ビットの数の最下位ビット, SR-b に格納された 4 ビットの数の最下位ビット, および D フリップフロップ DFF。 に格納された 1 ビット  $c_4$  を加算し, sum を SR-a の最上位ビットに, carry を D フリップフロップ DFF。 に格納する.

- 3: 縦続接続された 4 個の D フリップフロップ  $DFF_3$ ,  $DFF_2$ ,  $DFF_1$ ,  $DFF_0$  から成る部分回路を 4 カウンタと呼ぶと, これは以下の機能を有する.

- (0) (0000) なる4ビットを同時に入力する

- (1) 右に1ビットシフトし、最上位ビットに入力1を取り込む

- 4: D フリップフロップ DFF。は以下の機能を有する.

- (0) 格納している値を再度取り込む

- (1) 全加算器 FA の出力 carry をを取り込む

- 5: Ovf を保持する D フリップフロップの値は、Ovf =  $c_4 \oplus carry$  であるから、この値を見ることにより、 2 の補数表現された 4 ビットの加算がオーバーフローしたか否かを検出できる.

従って、このデータパス部に問題で指示された動作を行わせるには、以下の手順を実行すればよいことが分かる。その手順をプログラム風に書くと以下のようになる。

- 0°: 制御入力 start が 1 になるまで待機し, 1 になったら次に行く.

- 1°: シフトレジスタ SR-a の全ビットを 0 にする.

- 2°: 加算すべき 4 ビットの数  $\mathbf{a}_i = (\mathbf{a}_{i3} \, \mathbf{a}_{i2} \, \mathbf{a}_{i1} \, \mathbf{a}_{i0})_2^{2C}$  をシフトレジスタ SR-b に入れると共に 4 カウンタに  $(0\,0\,0\,0)$  を入れる.

- 3°: SR-a の最下位ビット, SR-b の最下位ビット, および  $c_4$ を加算し, sum を SR-a の最上位ビットに, carry を D フリップフロップ DFF。に、Ovf の値を D フリップフロップ DFF に入れた後、SR-a、SR-b、および 4 カウンタを右に 1 ビットシフトする.

- 4°: 4 カウンタの最下位ビット  $d_0$  が 0 ならば 3° に戻り、1 ならば(すなわち、3° の操作を 4 回実行したならば)、Ovf の値に応じて次の操作を行う.

- $5^{\circ}$ : Ovf = 0 ならば  $2^{\circ}$  に戻り, 1 ならば, 結果を出力して  $0^{\circ}$  に戻る.

#### (i) ミーリ型順序回路

上記の手順から、ミーリ型順序回路(ミーリ型有限状態機械、7 章 7.3)の状態遷移表および出力表として、下表のようなものを考えればよいことが分かる. もちろん、これは 1 例であって、他にも考えられる.

|            | 状態    | 遷移表                  |            | 出力表     |                               |                                                  |                                                                          |                                                                                |      |  |

|------------|-------|----------------------|------------|---------|-------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|--|

| 現状態        | 制御入力  | ステータ<br>ス信号          | 次状態        | 動作      | 制御信号                          |                                                  |                                                                          |                                                                                |      |  |

| 態          | start | d <sub>0</sub> , Ovf | 態          |         | CSa1, CSa0                    | CSb1, CSb0                                       | CScry                                                                    | CScnt                                                                          | done |  |

|            | 0     | -, -                 | S0         | 待機      | *, *                          | *, *                                             | *                                                                        | *                                                                              | 0    |  |

| S0         | 1     | -, -                 | <b>S</b> 1 | 初期<br>化 | 0, 1<br>SR-a' :=<br>(0 0 0 0) | *, *                                             | *                                                                        | *                                                                              | 0    |  |

| <b>S</b> 1 | -     | -, -                 | S2         | 入力      | 0,0<br>変化無し                   | 0, 1<br>$SR-b' := (a_{i3} a_{i2} a_{i1} a_{i0})$ | $ \begin{array}{c} 0 \\ c \leftarrow 0, \\ c_4' := c_4 \end{array} $     | $0 \\ (d_3 d_2 d_1 d_0)' \\ := (0 0 0 0)$                                      | 0    |  |

|            | _     | 0, -                 | S2         | 加算      | 1, 1<br>shift-right           | 1, 1<br>shift-right                              | $ \begin{array}{c} 1 \\ c \leftarrow c_4, \\ c_4' := carry \end{array} $ | $ \begin{array}{c} 1 \\ (d_3 d_2 d_1 d_0)' \\ := (1 d_3 d_2 d_1) \end{array} $ | 0    |  |

| S2         | _     | 1, 0                 | S2         | 入力      | 0,0 変化無し                      | $0, 1$ $SR-b' := (a_{i3} a_{i2} a_{i1} a_{i0})$  | $0$ $c \leftarrow 0,$ $c_4' := c_4$                                      | $0 \\ (d_3 d_2 d_1 d_0)' \\ := (0 0 0 0)$                                      | 0    |  |

|            | _     | 1, 1                 | S0         | 出力      | 0,0<br>変化無し                   | 0,0<br>変化無し                                      | $0$ $c \leftarrow 0,$ $c_4' := c_4$                                      | *                                                                              | 1    |  |

今、状態の個数は 3 個なので、2 つの状態変数 v、w を用い、初期状態 S0 を (v,w) = (0,0) とする. そうすると、これらを格納する D フリップフロップとして、値を 0 に初期化できるリセット入力付きの D フリップフロップ (5 章演習問題 [4] の図 5.3)を用いることができる. ただし、これらの状態を格納するための D フリップフロップの初期化 (値を 0 にする)操作は、上に示した状態遷移図の動作を行わせるより前に行っておかねばならない。

さらに、S1 および S2 の符号を下の表のように状態割り当てすると、状態遷移表および出力表は下のようになる.

|             | 状態:   | 遷移表                  |                   | 出力表   |       |       |       |      |  |  |

|-------------|-------|----------------------|-------------------|-------|-------|-------|-------|------|--|--|

| 現状態<br>v, w | 制御入力  | ステータ<br>ス信号          | - 次状態 ·<br>v', w' | 制御信号  |       |       |       |      |  |  |

|             | start | d <sub>0</sub> , Ovf |                   | CSa1, | CSb1, | CScry | CScnt | done |  |  |

|             |       |                      |                   | CSa0  | CSb0  | CSCIY |       |      |  |  |

| S0          | 0     | -, -                 | S0<br>0, 0        | *, *  | *, *  | *     | *     | 0    |  |  |

| 0, 0        | 1     | -, -                 | S1<br>0, 1        | 0, 1  | *, *  | *     | *     | 0    |  |  |

| S1<br>0, 1  | 1     | -, -                 | S2<br>1, 0        | 0, 0  | 0, 1  | 0     | 0     | 0    |  |  |

|             | _     | 0, –                 | S2<br>1, 0        | 1, 1  | 1, 1  | 1     | 1     | 0    |  |  |

| S2<br>1, 0  |       | 1, 0                 | S2<br>1, 0        | 0, 0  | 0, 1  | 0     | 0     | 0    |  |  |

|             | _     | 1, 1                 | S0<br>0, 0        | 0, 0  | 0, 0  | 0     | *     | 1    |  |  |

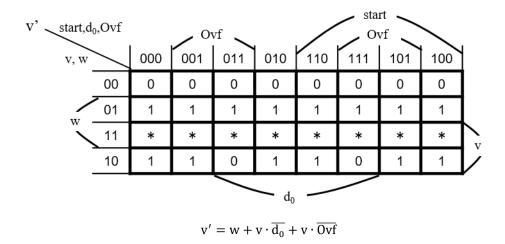

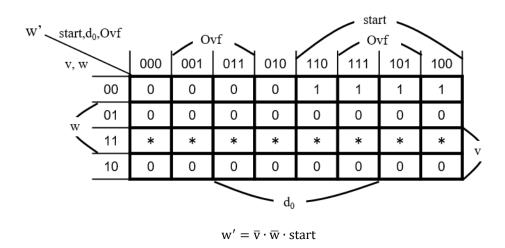

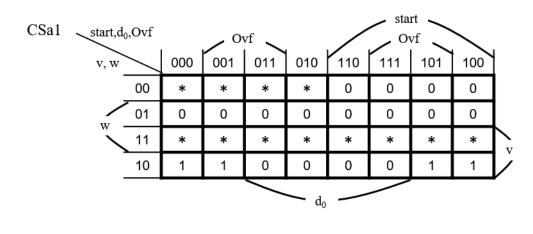

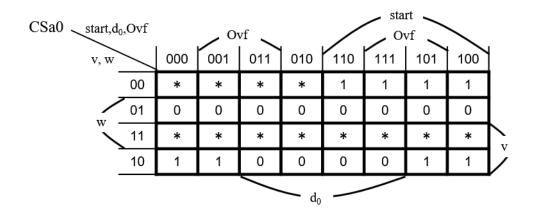

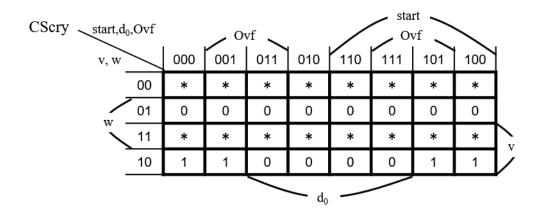

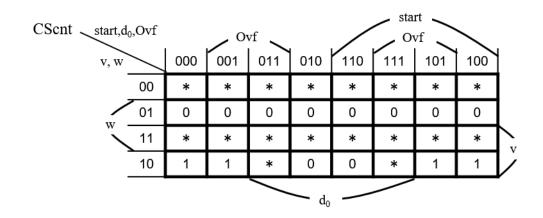

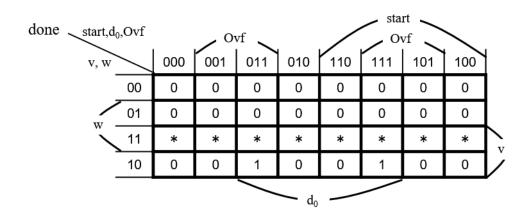

これより、 $\mathbf{v}$ ' および  $\mathbf{w}$ ' のカルノー図は下図のようになり、これらより、 $\mathbf{v}$  および  $\mathbf{w}$  の状態方程式が得られる.

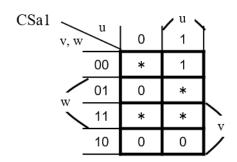

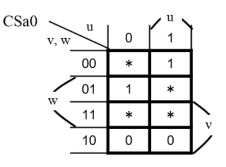

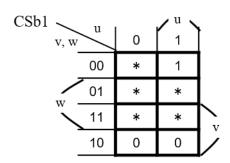

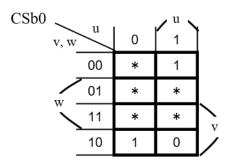

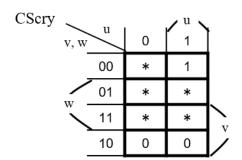

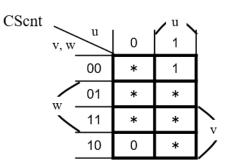

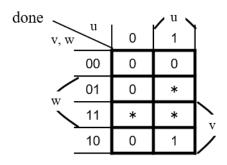

さらに、各出力のカルノー図および出力方程式は下のようになる.

$CSa1 = v \cdot \overline{d_0}$

$CSa0 = \overline{v} \cdot \overline{w} + v \cdot \overline{d_0}$

$\mathsf{CSb1} = v \cdot \overline{d_0}$

$CSb0 = w + v \cdot \overline{Ovf}$

$$\mathsf{CScry} = v \cdot \overline{d_0}$$

$\mathsf{CScnt} = v \cdot \overline{d_0}$

$done = v \cdot d_0 \cdot Ovf$

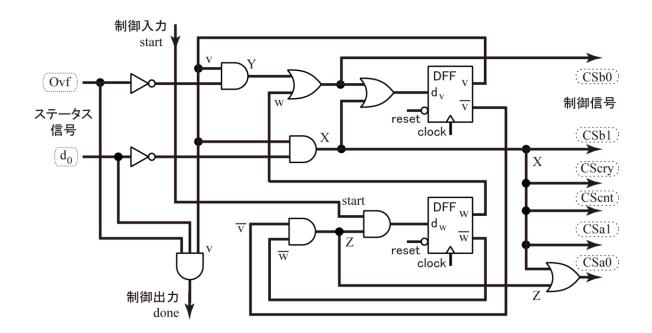

そこで、状態変数 v および w の値を格納する D フリップフロップの入力変数をそれぞれ  $d_v$  および  $d_w$  とする と、これらおよび各出力は、

$$X = v \cdot \overline{d_0}$$

,  $Y = v \cdot \overline{Ovf}$ ,  $Z = \overline{v} \cdot \overline{w}$

とすると, 次式で決定できる.

### ディジタル回路設計 <第8章:集積回路設計> 解答例

$$\begin{split} d_v &= w + v \cdot \overline{d_0} + v \cdot \overline{Ovf} = w + X + Y = X + CSb0 \ , \qquad d_w = \overline{v} \cdot \overline{w} \cdot start = Z \cdot start \\ & CSa1 = v \cdot \overline{d_0} = X \ , \qquad CSa0 = \overline{v} \cdot \overline{w} + v \cdot \overline{d_0} = Z + X \\ & CSb1 = v \cdot \overline{d_0} = X \ , \qquad CSb0 = w + v \cdot \overline{Ovf} = w + Y \\ & CScry = v \cdot \overline{d_0} = X \ , \qquad CScnt = v \cdot \overline{d_0} = X \ , \qquad done = v \cdot d_0 \cdot Ovf \end{split}$$

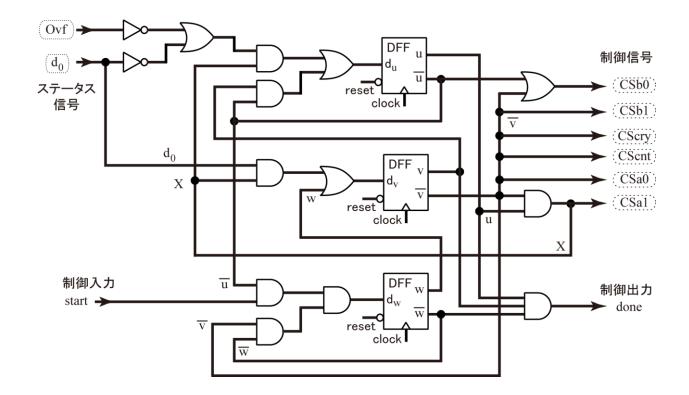

これらより、下図のような回路を得る.この回路では、論理ゲートの個数を減らすため、共通論理式を利用して回路の多段化(4章4.10)が行われているため、出力回路と状態遷移回路が渾然となっているが、出力の値の決定に入力が用いられていることが分かるであろう.

#### (ii) ムーア型順序回路

ムーア型順序回路(ムーア型有限状態機械)の状態遷移表および出力表として、下記のような機能のものを考えれば、与えられたデータパス部に所望の動作を行わせることができる。もちろん、ミーリ型の順序回路の場合と同様 1 例であって、他にも考えられる。

|            | 状態    | 遷移表                  |            | 出力表    |                               |                                                  |                                     |                                           |      |  |

|------------|-------|----------------------|------------|--------|-------------------------------|--------------------------------------------------|-------------------------------------|-------------------------------------------|------|--|

| 現狀態        | 制御入力  | ステータ<br>ス信号          | 次状態        | 動      | 制御信号                          |                                                  |                                     |                                           |      |  |

| 態          | start | d <sub>0</sub> , Ovf | :能         | 作      | CSa1, CSa0                    | CSb1, CSb0                                       | CScry                               | CScnt                                     | done |  |

| 60         | 0     | -, -                 | S0         | 待機     |                               | ale ale                                          | *                                   | .1.                                       | 0    |  |

| S0         | 1     | -, -                 | S1         | 機      | *, *                          | *, *                                             | *                                   | *                                         | 0    |  |

| S1         |       | -, -                 | S2         | 初期化    | 0, 1<br>SR-a' :=<br>(0 0 0 0) | *, *                                             | *                                   | *                                         | 0    |  |

| S2         |       | _, _                 | <b>S</b> 3 | 入力     | 0,0<br>変化無し                   | 0, 1<br>$SR-b' := (a_{i3} a_{i2} a_{i1} a_{i0})$ | $0$ $c \leftarrow 0,$ $c_4' := c_4$ | $0 \\ (d_3 d_2 d_1 d_0)' \\ := (0 0 0 0)$ | 0    |  |

|            | _     | 0, -                 | S3         |        | 1 1                           | 1 1                                              | 1                                   | 1                                         |      |  |

| <b>S</b> 3 | _     | 1, 0                 | S2         | 加<br>算 | 1, 1                          | 1, 1                                             | $c \leftarrow c_4$                  |                                           | 0    |  |

|            |       | 1, 1                 | S4         |        | shift-right                   | shift-right                                      | $c_4' := carry$                     | $:= (1 d_3 d_2 d_1)$                      |      |  |

| S4         | _     | -, -                 | SO         | 出力     | 0,0<br>変化無し                   | 0,0<br>変化無し                                      | $0$ $c \leftarrow 0,$ $c_4' := c_4$ | *                                         | 1    |  |

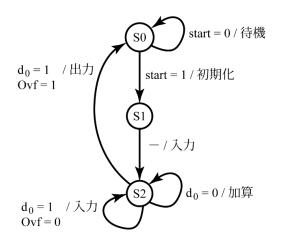

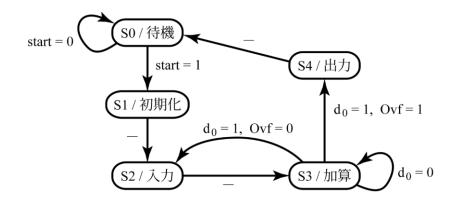

これらの表から得られる状態遷移図を下に示す.

## ディジタル回路設計 <第8章:集積回路設計> 解答例

今, 状態の個数は 5 個なので、3 つの状態変数 u, v, w を用い、初期状態 S0 を (u, v, w) = (0,0,0) として、リセット入力付きの D フリップフロップを用いてこれらの状態変数の値を格納する。 さらに、S1 から S4 の符号を下の表のように状態割り当てすると、状態遷移表および出力表は下のようになる。

|                | 状態    | <b></b><br>遙遷移表      |                   | 出力表           |               |       |           |      |  |

|----------------|-------|----------------------|-------------------|---------------|---------------|-------|-----------|------|--|

| 그런 시간 상순       | 制御入力  | ステータ<br>ス信号          | <b>火下・</b> イフ・    |               | 制御出力          |       |           |      |  |

| 現状態<br>u, v, w | start | d <sub>0</sub> , Ovf | 次状態<br>u', v', w' | CSa1,<br>CSa0 | CSb1,<br>CSb0 | CScry | CScn<br>t | done |  |

| S0             | 0     | _, _                 | S0<br>0, 0, 0     | *, *          | *, *          | *     | *         | 0    |  |

| 0, 0, 0        | 1     | -, -                 | S1<br>0, 0, 1     | *, *          | T, T          | 7,1   | *         | U    |  |

| S1<br>0, 0, 1  | _     | _, _                 | S2<br>0, 1, 0     | 0, 1          | *, *          | *     | *         | 0    |  |

| S2<br>0, 1, 0  | _     | _, _                 | S3<br>1, 0, 0     | 0, 0          | 0, 1          | 0     | 0         | 0    |  |

|                | _     | 0, -                 | S3<br>1, 0, 0     |               |               |       |           |      |  |

| S3<br>1, 0, 0  | _     | 1, 0                 | S2<br>0, 1, 0     | 1, 1          | 1, 1          | 1     | 1         | 0    |  |

|                |       | 1, 1                 | S4<br>1, 1, 0     |               |               |       |           |      |  |

| S4<br>1, 1, 0  | _     | _, _                 | S0<br>0, 0, 0     | 0, 0          | 0, 0          | 0     | *         | 1    |  |

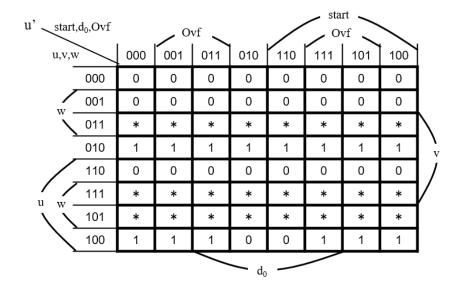

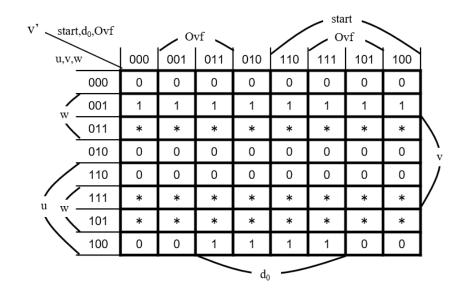

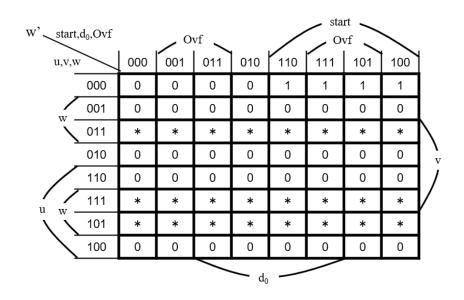

これより, u', v', および w' のカルノー図ならびにこれらの状態方程式が以下のように得られる.

$u' = v \cdot \overline{u} + u \cdot \overline{v} \cdot \overline{d_0} + u \cdot \overline{v} \cdot \overline{Ovf}$

$\mathbf{v}' = \mathbf{w} + \mathbf{u} \cdot \overline{\mathbf{v}} \cdot \mathbf{d}_0$

$w'=\bar{u}\cdot\bar{v}\cdot\bar{w}\cdot start$

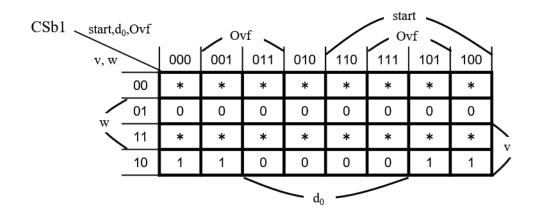

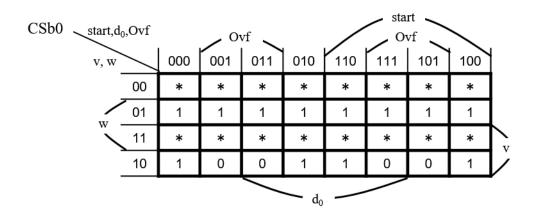

さらに、各出力のカルノ一図および出力方程式は下のようになる.

# ディジタル回路設計 <第8章:集積回路設計> 解答例

CSa1 =

$$\mathbf{u}\cdot \overline{\mathbf{v}}$$

あるいは CSa1 =  $\overline{\mathbf{v}}\cdot \overline{\mathbf{w}}$  CSa0 =  $\overline{\mathbf{v}}$

$$CSb1 = \bar{v}$$

$$\mathsf{CSb0} = \overline{\mathsf{v}} + \overline{\mathsf{u}}$$

$$CScry = \bar{v}$$

$$\mathsf{CScnt} = \overline{v}$$

done =  $u \cdot v \cdot \overline{w}$

そこで、状態変数 u, v, および w の値を格納する D フリップフロップの入力変数をそれぞれ  $d_u$ ,  $d_v$ , および  $d_w$  とすると、これらおよび各出力は、

$$X = u \cdot \overline{v}$$

とすると, 次式で決定できる.

$$\begin{split} d_u &= v \cdot \overline{u} + u \cdot \overline{v} \cdot \overline{d_0} + u \cdot \overline{v} \cdot \overline{Ovf} = v \cdot \overline{u} + X \cdot \left( \overline{d_0} + \overline{Ovf} \right) \\ d_v &= w + u \cdot \overline{v} \cdot d_0 = w + X \cdot d_0 \quad , \qquad \qquad d_w = \overline{u} \cdot \overline{v} \cdot \overline{w} \cdot \text{start} \\ & \text{CSa1} = u \cdot \overline{v} = X \quad , \qquad & \text{CSa0} = \overline{v} \\ & \text{CSb1} = \overline{v} \quad , \qquad & \text{CSb0} = \overline{v} + \overline{u} \\ & \text{CScry} = \overline{v} \quad , \qquad & \text{CScnt} = \overline{v} \quad , \qquad & \text{done} = u \cdot v \cdot \overline{w} \end{split}$$

従って,下図のような回路を得る.この回路では,出力の値は状態の値だけで決定される.