題意の回路を設計するために、以下の 3 状態  $Q_0$ ,  $Q_1$ ,  $Q_2$ を定義する.

| 状態             | 状態の説明        | 状態符号 q <sub>1</sub> , q <sub>2</sub> |  |

|----------------|--------------|--------------------------------------|--|

| $\mathbf{Q}_0$ | 1が1個も入ってない状態 | 0, 0                                 |  |

| $\mathbf{Q}_1$ | 1が1個入った状態    | 0, 1                                 |  |

| $\mathbf{Q}_2$ | 1が2個入った状態    | 1, 0                                 |  |

また、reset 入力付き D フリップフロップを利用できるので、2 つの状態変数  $q_1$ 、 $q_2$ を用い、初期状態  $Q_0$ を  $q_1=0$ 、 $q_2=0$  として、状態符号を上の表に示したように割り当てる。このとき、 $Q_0$  以外の状態には異なる符号を割り当てることもできる。

これらを利用すれば、所望の 3 カウンタの状態遷移表および出力表は以下のように書ける. なお、この表には、状態を表す記号  $(Q_0, Q_1, Q_2)$  と状態符号の両方を書いている.

| 現状態                             |      | 次状態   | q <sub>1</sub> ', q <sub>2</sub> ' | 出力 z |      |

|---------------------------------|------|-------|------------------------------------|------|------|

| q <sub>1</sub> , q <sub>2</sub> | 入力 x | 0     | 1                                  | 0    | 1    |

| $Q_0$                           |      | $Q_0$ | $Q_1$                              | 0    | 0    |

| 0, 0                            |      | 0, 0  | 0, 1                               |      |      |

| $Q_1$                           |      | $Q_1$ | $Q_2$                              | 0    | 0    |

| 0, 1                            |      | 0, 1  | 1, 0                               |      |      |

| $Q_2$                           |      | $Q_2$ | $Q_0$                              | 0 1  |      |

| 1, 0                            |      | 1, 0  | 0, 0                               | U    | •    |

| 1, 1                            |      | *, *  | *, *                               | *, * | *, * |

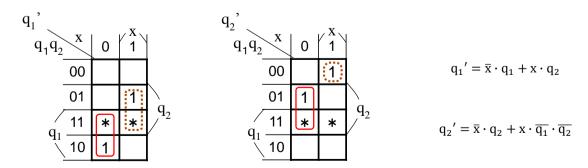

この状態遷移表から,次状態  $q_1$ ', $q_2$ ' のカルノー図が下図のように得られ,これらのカルノー図より, $q_1$ ', $q_2$ ' の最簡な積和型論理式が得られる.

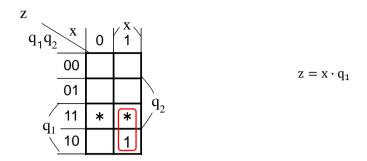

また, 出力表から, 出力 z のカルノー図と最簡な積和型論理式が下記のように得られる.

そこで、状態変数  $\mathbf{q}_1$  および  $\mathbf{q}_2$ ' を格納する DFF のデータ入力をそれぞれ  $\mathbf{d}_1$  および  $\mathbf{d}_2$  とすると、これらの入力方程式が以下のように得られる.

$$\begin{split} d_1 &= \overline{x} \cdot q_1 + x \cdot q_2 = \overline{\overline{x} \cdot q_1 + x \cdot q_2} = \overline{(\overline{x} \cdot q_1) \cdot (\overline{x} \cdot \overline{q_2})} \\ \\ d_2 &= \overline{x} \cdot q_2 + x \cdot \overline{q_1} \cdot \overline{q_2} = \overline{\overline{x} \cdot q_2 + x \cdot \overline{q_1} \cdot \overline{q_2}} = \overline{(\overline{x} \cdot q_2) \cdot (\overline{x} \cdot \overline{q_1} \cdot \overline{q_2})} \end{split}$$

また, 出力 z の出力方程式も NAND を用いて下記のように書ける.

$$z=x\cdot q_1=\overline{(\overline{x\cdot q_1})}$$

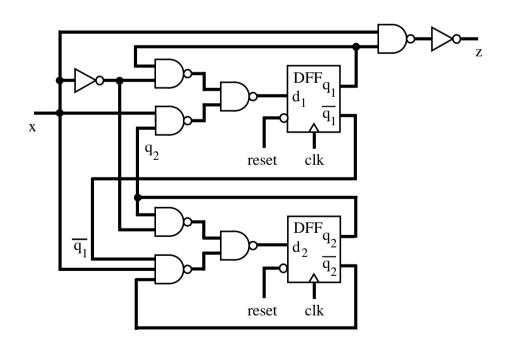

これらの式より,以下の回路が得られる.